Der ultimative RISC-Prozessor (URISC)

Im Rahmen des VLSIEntwurfspraktikum für SemiCustomChips in der

Abteilung

Entwurf integrierter

Schaltungen (E.I.S.)

entwickelte ich zusammen mit Frank Gerberding und Marc Zimmermann einen

Mikroprozessor, der nur einen einzigen Befehl beherscht: MOVE. Dieser

Befehlsvorrat läßt sich nicht weiter reduzieren, es ist also ein

ultimativ reduzierter Befehlssatz (und der Chip daher ein ultimatively

reduced instruction set computer, also ein U-RISC bzw. SIC - single instruction

computer).

Dass dieser Chip dennoch ein vollwertiger Rechner ist, verdankt er seiner

Arithmetisch-Logischen Einheit (ALU), die in den unteren Speicherbereich

eingeblendet wird: Der Zugriff auf bestimmte Adressen schreibt bzw. liest Daten

in die / aus der ALU und stößt dort automatisch die Berechnung

an. Sprünge sind möglich, indem eine neue Adresse in den

Programmzähler (PC) geschoben wird. Durch die geschickte Verwendung von

Flag-Operationen (Überlauf, Null, Negativ und Kombinationen daraus) sind

sogar bedingte Spünge, auch eine Vorraussetzung für Schleifen, leicht

realisierbar.

Im Rahmen des VLSIEntwurfspraktikum für SemiCustomChips in der

Abteilung

Entwurf integrierter

Schaltungen (E.I.S.)

entwickelte ich zusammen mit Frank Gerberding und Marc Zimmermann einen

Mikroprozessor, der nur einen einzigen Befehl beherscht: MOVE. Dieser

Befehlsvorrat läßt sich nicht weiter reduzieren, es ist also ein

ultimativ reduzierter Befehlssatz (und der Chip daher ein ultimatively

reduced instruction set computer, also ein U-RISC bzw. SIC - single instruction

computer).

Dass dieser Chip dennoch ein vollwertiger Rechner ist, verdankt er seiner

Arithmetisch-Logischen Einheit (ALU), die in den unteren Speicherbereich

eingeblendet wird: Der Zugriff auf bestimmte Adressen schreibt bzw. liest Daten

in die / aus der ALU und stößt dort automatisch die Berechnung

an. Sprünge sind möglich, indem eine neue Adresse in den

Programmzähler (PC) geschoben wird. Durch die geschickte Verwendung von

Flag-Operationen (Überlauf, Null, Negativ und Kombinationen daraus) sind

sogar bedingte Spünge, auch eine Vorraussetzung für Schleifen, leicht

realisierbar.

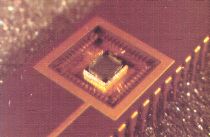

Dieser Chip wurde im Anschluß an das Praktikum in der enormen

Stückzahl 10 (in Worten: zehn) gefertigt. Eines dieser Exemplare ist auf

den beiden Bildern hier zu sehen (sie sind direkt vom Dia gescannt, daher ist

die Qualität etwas dürftig...).

Dieser Chip wurde im Anschluß an das Praktikum in der enormen

Stückzahl 10 (in Worten: zehn) gefertigt. Eines dieser Exemplare ist auf

den beiden Bildern hier zu sehen (sie sind direkt vom Dia gescannt, daher ist

die Qualität etwas dürftig...).

Die internen Berechnungen hätten noch bei einer Taktrate von 90MHz (jaja, heute lacht man darüber...) zuverlässig funktioniert, leider war diesen Geschwindigkeiten jedoch die (nicht von uns zu verantwortende) Datenübertragung vom Chip an die Peripherie (und umgekehrt) nicht mehr gewachsen, weshalb er insgesamt nur mit 50MHz getaktet werden konnte, da die Abarbeitung eines MOVE Befehls vier Taktzyklen benötigte (Quelladresse aus Programmcode lesen, Daten auslesen, Zieladresse lesen, Daten schreiben), waren also 12.5 * 106 Verschiebungen pro Sekunde möglich.